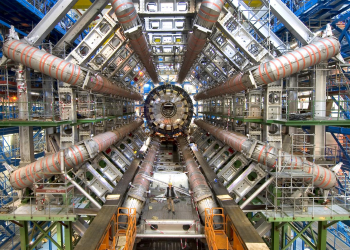

NVIDIA анонсировала процессор Vera в качестве отдельной SoC, доступной для сторонних разработчиков как альтернатива Intel Xeon и AMD EPYC. Однако при взаимодействии с GPU AMD или другими производителями могут возникать трудности.

Технический сбой приводит к ошибкам при использовании видеокарт или AI-ускорителей других марок. Проблема связана с тем, как контроллеры PCIe процессоров Vera создают адреса памяти. В определённых условиях они могут генерировать недействительные адреса, нарушая стабильное соединение со сторонними устройствами. Это происходит во время записи PCIe Memory-Mapped I/O (MMIO), когда процессор пытается записать данные с частичным байтовым разрешением в область MMIO.

Проблема усложняется, когда эти области используют атрибут Arm Normal Non-Cacheable памяти «MT_NORMAL_NC», что создает значительные трудности с совместимостью. Так как Arm применяет более гибкий порядок обработки памяти для обычных некэшируемых атрибутов, это может вызвать ошибку, приводящую к неправильной генерации адресов, повреждению данных и даже сбоям устройств PCIe при выполнении высокоинтенсивных нагрузок с DMA, например, в процессе обучения искусственного интеллекта или моделирования HPC. GPU NVIDIA адаптированы с учетом требований Vera и особенностей их доступа к памяти, поэтому проблем не возникает.

Как отмечает TechPowerUp, NVIDIA может устранить эту проблему с использованием своих специализированных ядер Linux, в которых предусмотрены обходные пути для таких случаев. В NV-Kernels, которые NVIDIA поддерживает в отдельном репозитории для своей аппаратуры, есть патч для ядра Linux, трансформирующий MT_NORMAL_NC в Device-nGnRE (non-Gathering, non-Reordering, Early acknowledgement), что обеспечивает более строгий порядок обработки. Хотя производительность в основном сохраняется, могут возникнуть задержки, которые могут негативно сказаться на некоторых работах, чувствительных к вводу/выводу.

Эта проблема затрагивает не только процессоры NVIDIA. Контроллеры PCIe систем Ampere Computing Altra на базе Arm также генерируют недействительные адреса при записи MMIO в определённых сценариях. Ampere решает эту проблему аналогичным образом, что может указывать на то, что главная причина заключается в обработке памяти Arm при подключении внешних устройств. Тем не менее, о снижении производительности пока не сообщалось.